Todays complex electrical architectures have grown far beyond traditional circuits. They now include microcontrollers, sensors, and communication buses, all interconnected through intricate harnesses. Diagnosing faults in such systems requires more than guesswork or observationit demands a logical process supported by accurate tools. Without a clear diagnostic framework, troubleshooting quickly turns into trial-and-error that wastes both time and components.

Diagnostics is the systematic study of system behavior. It observes how a system performs under design conditions compared to reality. Success begins by defining known-good baselines: voltage, waveform, or logic state. Each data point captured offers clues that, when combined, reveal the precise fault origin.

### **1. Fundamental Tools**

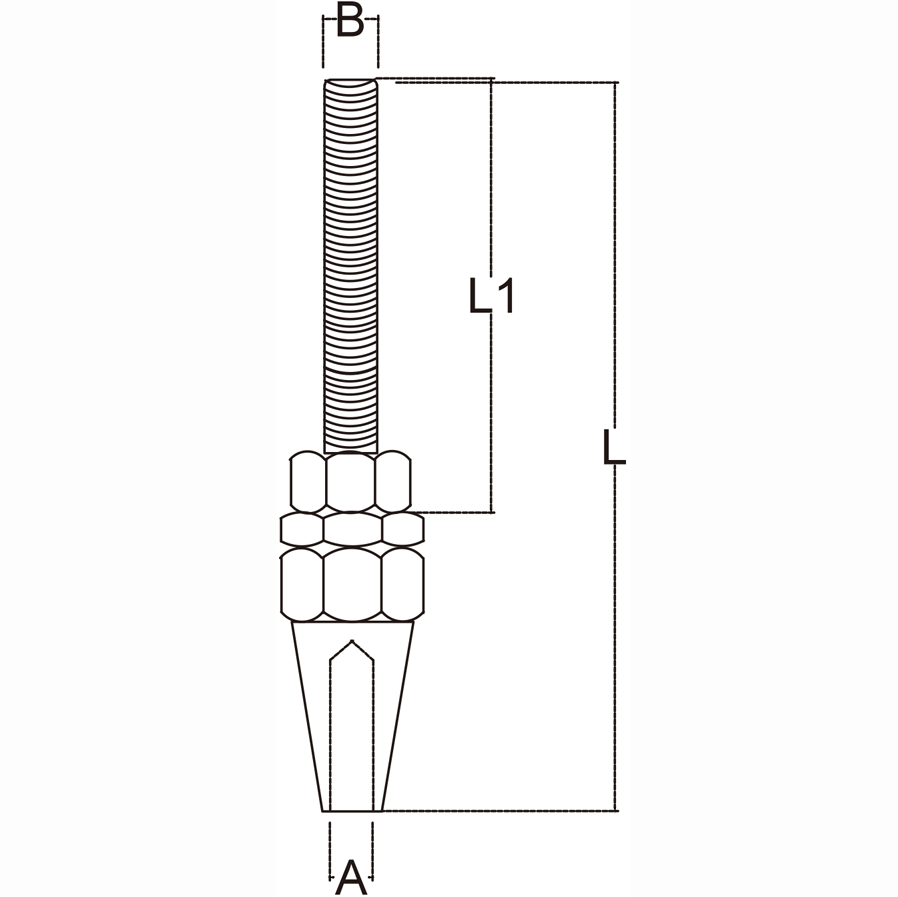

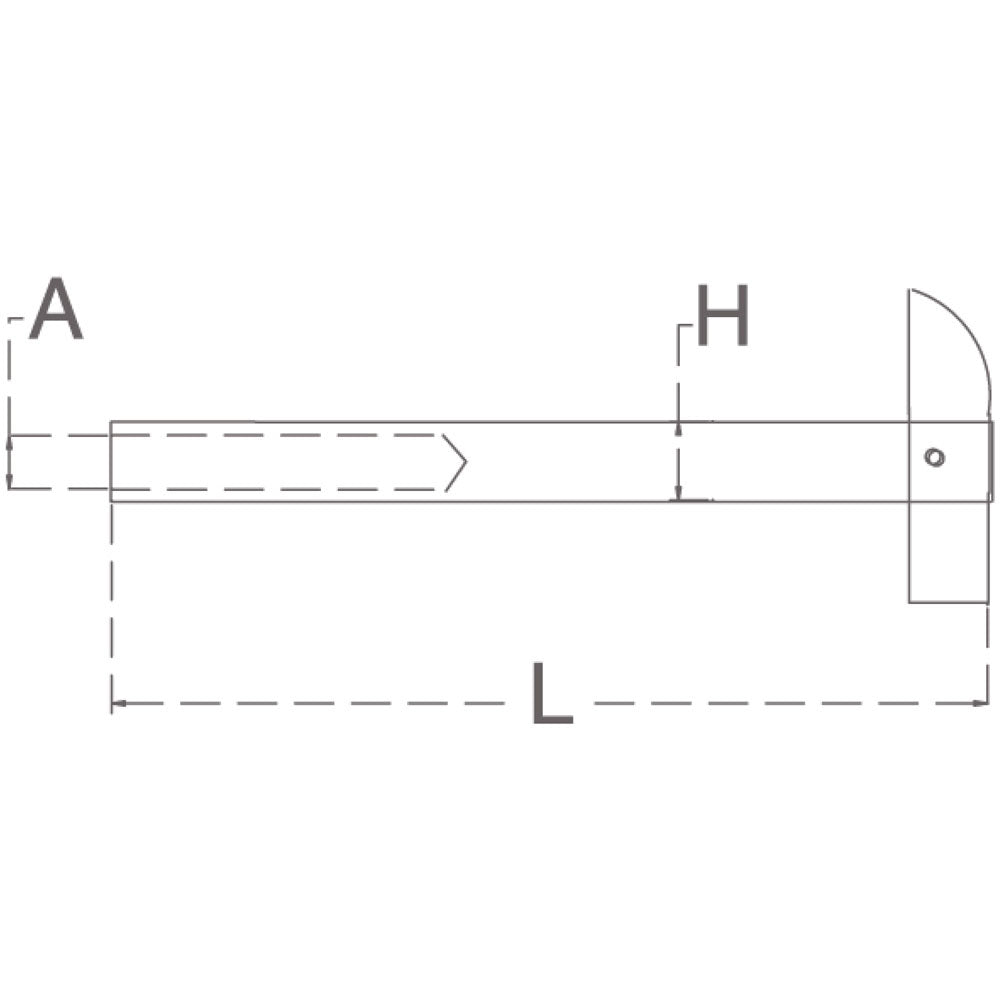

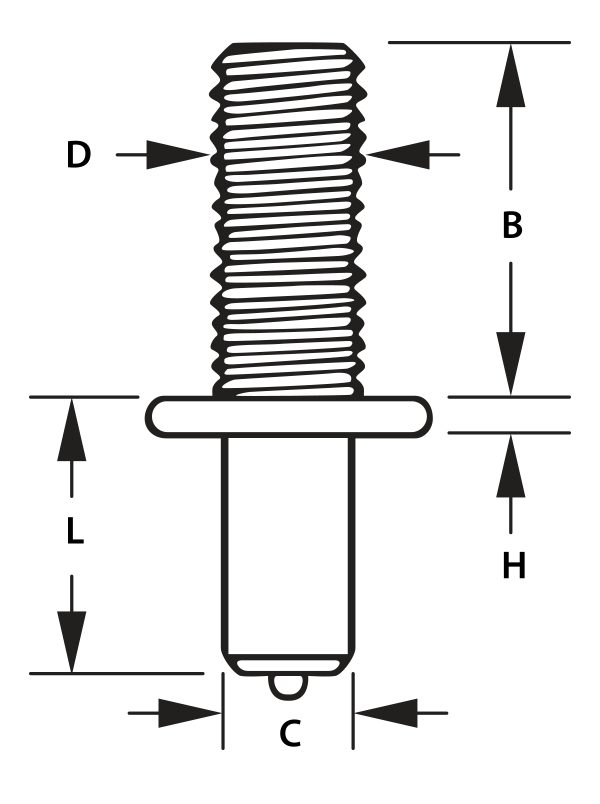

The starting point of every diagnostic process is the digital multimeter (DMM). It measures the three key electrical quantities with accuracy and repeatability. Whether youre checking battery supply, ground integrity, or sensor feedback, the DMM provides the first layer of confirmation. Its beeper and forward-bias tests quickly expose broken links or polarity faults.

The scope extends measurement into the dynamic realm. It reveals how voltage changes with time, displaying pulses, oscillations, and switching behaviors. For PWM, communication, or switching regulators, oscilloscopes visualize distortion, missing pulses, or delay. Multi-channel scopes can compare input and output to assess propagation delay or synchronization.

non-contact current tools measure current without breaking circuits. They use field sensing to detect current magnitude and direction, ideal for energized installations. Modern DC-capable models reveal inrush or leakage current that static tests may miss.

### **2. Advanced Diagnostic Instruments**

When basic tools arent enough, technicians turn to specialized analyzers and testers. digital decoders capture serial communication like CAN, LIN, or UART, translating bits into structured messages. This is vital when controllers exchange information and voltage readings alone cant explain failures.

Insulation resistance testers (megohmmeters) apply DC stress tests to detect leakage or weak insulation. In critical systems, this prevents catastrophic insulation failure.

Cable analyzers locate distance-to-fault in cables. Theyre indispensable for high-end communication cables.

At component level, precision analyzers measure electrical parameters with high accuracy. This detects degraded capacitors. Thermal cameras visualize heat signatures, instantly exposing hotspots invisible to meters.

### **3. Measurement Strategy**

Tools mean little without method and order. Effective troubleshooting follows a repeatable workflow:

- **Visual Inspection:** Look for physical damage, wear, or contamination. Over half of faults are found visually.

- **Power & Ground Verification:** Confirm voltage supply and low resistance returns. Many faults hide in poor grounds.

- **Signal Analysis:** Compare transitions and duty cycles during real operation.

- **Comparative Testing:** cross-check similar circuits.

- **Functional Simulation:** Replicate operating conditions to confirm repairs.

Record every reading. Documentation builds a diagnostic history, turning data into predictive maintenance.

### **4. Safety and Calibration**

Safety ensures accuracy. Before testing, inspect probes and leads. verify meter and scope performance regularly to avoid drifted readings. Always respect safety categories: never use a low-rated meter on high-energy systems. For high-voltage or floating circuits, use differential probes, isolation transformers, or optically isolated links.

### **5. Data Integration and Modern Trends**

Diagnostics is becoming digitally connected. Wireless multimeters and smart oscilloscopes stream data directly to the cloud. This enables remote monitoring, predictive analytics, and fault trending. Automated Test Systems (ATS) now perform mass verification cycles, ensuring standardized quality. Combined with machine learning algorithms, they predict weak points before failures occur.

### **6. The Human Element**

Despite automation, the technicians judgment stays vital. Instruments show numbers, but expertise gives context. Skilled engineers correlate symptoms, readings, and history. They know that a strange voltage or waveform may be a symptom, not the root cause. Effective diagnosis balances logic and intuition.

Ultimately, the goal is not just to collect data, but to understand. The right tools extend human senses, turning electrical behavior into a readable story. Good diagnostics transforms random faults into predictable phenomenathe essence of intelligent troubleshooting.